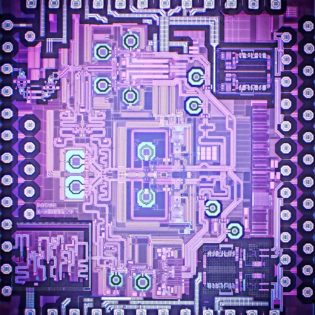

La plate-forme Conception de circuits intégrés

La Plate-forme Conception de circuits intégrés, installée dans le bâtiment des composants avancés, regroupe 150 spécialistes des architectures, de la conception de circuits numériques, analogiques, mixtes et RF, sur silicium bulk, SOI et Organique. Elle intègre également des spécialistes du logiciel embarqué et est connectée à la plateforme systèmes embarqués du Campus Paris-Saclay.

Elle dispose d’une large palette d’outils de CAO (Cadence, Mentor Graphics, Synopsys, Agilent…), de moyens d’émulation et de moyens de test et de caractérisation. Son budget de fonctionnement annuel s’élève à plus de 10 millions d’euros.

Sa taille et son niveau d’équipement en font le pôle de conception le plus important d’Europe. Elle dispose en particulier d’une expertise reconnue en matière d’architectures System on Chip (SOC), d’architectures et circuits radiofréquences, d’architectures et circuits analogiques et mixtes pour circuits d’imagerie ou interfaces capteurs, de transistors couches minces SOI ou de nouveaux concepts de MOS ou d’assemblage 3D et de photonique sur silicium.

L’activité de la plate-forme comprend des collaborations avec des laboratoires de MINATEC, des partenariats avec les industriels et des participations à des programmes de recherche : ANR, AII, clusters EUREKA, FP7, pôles de compétitivité, etc. Certains de ces projets peuvent impliquer plus d’une dizaine d’hommes/an pendant plusieurs années.

Les circuits conçus au sein de la plate-forme sont destinés à des domaines applicatifs très variés : télécoms, automobile, multimédia, santé, défense etc.

Contact : severine.vignoud@cea.fr

Contactez-nous

Contactez-nous Plan d’accès

Plan d’accès