Système de mesure intégré sub-millimétrique 4 ports

Publié le : 4 juin 2018

Candidature à une bourse ministérielle Candidature à une bourse ministérielle

RFIC -Lab /IEMN /IEMN

Laboratoire de Radio-Fréquences et d’ Intégration de Circuits (en création)

Institut d’Electronique de Microélectronique et de Nanotechnologie

Sujet de Thèse

Système de mesure intégré sub Système de mesure intégré sub-millimétrique millimétrique 4port

Mots clés : Mesure millimétrique in-situ, caractérisation petit signal intégré

1. Contexte : problématique des mesures dans le domaine sub-millimétrique

Depuis 2003, les applications de type radar (imagerie et sécurité dans les aéroports, (imagerie et sécurité dans les aéroports, imagerie médicale, détection de tumeur, dépistage génétique) et communication sans fil (inter-satellite et spatiale) ont connu une évolution croissante au fil des années. Que ce soit en termes de résolution pour les radars ou en termes de débit pour les communications sans fil, qui sont de plus en plus élevés, la bande passante des circuits mise en jeu doit obligatoirement augmenter (théorème de Shannon). Aujourd’hui, avec l’apparition de technologies photoniq Shannon). Aujourd’hui, avec l’apparition de technologies photoniq Shannon). Aujourd’hui, avec l’apparition de technologies photoniq Shannon). Aujourd’hui, avec l’apparition de technologies photoniq Shannon). Aujourd’hui, avec l’apparition de technologies photoniq Shannon). Aujourd’hui, avec l’apparition de technologies photoniq Shannon). Aujourd’hui, avec l’apparition de technologies photoniq Shannon).

Aujourd’hui, avec l’apparition de technologies photoniques sur silicium, la nécessité d’avoir des circuits électroniques fonctionnant au -delà de 110 GHz apparait comme nécessaire. Aux fréquences millimétriques, les méthodes classiques de caractérisation de dispositifs microélectroniques intégrés sont réalisées à l’aide d’un analyseur vectoriel de réseaux (AVR) et de pointes de mesure. Au -delà de 110 GHz, les mesures petits signaux (paramètres S) posent de réelles difficultés alors qu’elles donnent bons résultats jusqu’à 110 GHz [1]. Pour accéder aux paramètres S du Dispositif Sous Test (DST), ces techniques consistent à calibrer l’AVR consistent à calibrer l’AVR consistent à calibrer l’AVR consistent à calibrer l’AVR consistent à calibrer l’AVR consistent à calibrer l’AVR consistent à calibrer l’AVR consistent à calibrer l’AVR consistent à calibrer l’AVR consistent à calibrer l’AVR consistent à calibrer l’AVR consistent à calibrer l’AVR consistent à calibrer l’AVR au niveau des pointes de mesures puis une étape d’épluchage (de une étape d’épluchage (deune étape d’épluchage (deune étape d’épluchage (de une étape d’épluchage (deune étape d’épluchage (deune étape d’épluchage (de -embedding) permet de s’affranchir des effets parasites des plots de mesure et des lignes d’accès. Ces méthodes d’ épluchage sont limitées en fréquence. En effet , elles prennent difficilementen compte les en compte les effets de couplage (entre les pointes de mesure et le substrat) ainsi les discontinuités engendrées par les accès [2].

De plus , il n’existe aucun appareil commercial de caractérisation qui soit capable de mesurer les paramètres S directement avec 4 ports au -delà delà delà de 140 GHz .

2. Solution investiguée : conception d’un système de mesure intégré

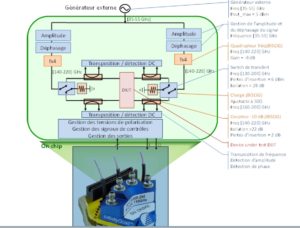

La solution que nous proposons consiste à intégrer une partie du système de mesure directement dans le wafer, au plus près du DUT. Cette solution est similaire à un AVR dont une partie serait intégrée sur silicium. L’avantage de cette solution est qu’elle permet d’injecter dans le wafer un signal à des fréquences raisonnables entre 35 et 55 GHz. Ensuite ces fréquences peuvent être quadruplées dans le wafer en intégrant un multiplieur de fréquence à l’entrée du DUT. Afin d’atteindre les spécifications requises pour ce système au-delà de 110 GHz, il sera nécessaire de travailler avec une technologie avancée qui donne de bonnes performances en terme de pertes (nécessité d’avoir des conducteurs épais dans les couches métalliques supérieures) et de bruit dans le domaine sub-millimétrique. Un certain nombre de blocs élémentaires de ce système ont déjà été réalisés par différents doctorants (conception à l’IMEP-LAHC et caractérisation à l’IEMN). Ces blocs ont été conçus en technologie BiCMOS HBT SiGe 55nm de STMicroelectronics [3-7] dans le cadre du projet ANR 2014-2018 BISCIG soutenu par l’Agence Nationale de la Recherche (http://biscig.grenoble-inp.fr/). Cette technologie est extrêmement performante en bande millimétrique, aussi bien au niveau du Back End pour les circuits passifs (métaux épais) qu’au niveau du Front End pour les circuits actifs (fT/fmax=300/400 GHz). Ces blocs doivent être maintenant correctement assemblés et optimisés pour réaliser un véritable système de mesure performant qui n’existe pas encore sur le marché.

3. Sujet de thèse, objectifs et collaborations

Le doctorant devra concevoir ce système complet de mesure 4 ports, petits signaux en full differential (Figure 1) en technologie BiCMOS 55nm pour des fréquences comprises entre 140 et 220 GHz (Bande G) en s’appuyant sur les travaux déjà réalisés dans cette thématique.

L’objectif à terme est d’intégrer tout le système de mesure dans la pointe de mesure RF.

Le doctorant travaillera au RFIC-Lab en étroite collaboration avec la société STMicroelectronics qui fournit la technologie BiCMOS 55nm et au laboratoire IEMN à Lille où la caractérisation des circuits s’effectuera.

Figure 1 Système de mesure millimétrique intégré quatre ports différentiels [140-220] GHz où les blocs élémentaires déjà conçus sont en orange, les blocs à concevoir en bleu.

4. Profil du candidat

Des compétences en conception électronique analogique sous Cadence et ADS seront nécessaires pour mener à bien ce travail.

5. Contacts

Merci d’envoyer un CV et une lettre de motivation (avant le 5 juin 2018 ) à :

Jean-Daniel ARNOULD, 04.56.52.95.59. jean-daniel.arnould@grenoble -inp.fr

Estelle LAUGA-LARROZE, 04.56.52.94.80, estelle.lauga – larroze@univ -grenoble-alpes.fr

Christophe GAQUIERE, 03.20.19.78.29, christophe.gaquiere@iemn.univ -lille1.fr

6. Bibliographie

[1] B. Zhang, et al. et al. « On the De -Embedding Issue of Millimeter-Wave and Sub-Millimeter -Wave Measurement and Circuit Design », IEEE Trans. on Comp., Pack. and Manufact. Tech., vol. 2, no 8, pp. 1361-1369, 2012.

[2] N. Derrier, et al. « State-of -the-art and future perspective and de-embedding techniques for characterization of advanced SiGe HBTs featuring sub-THz fT/fMAX », in 2012 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM) 2012, pp. 1-8.

[3] X. -L. Tang et al. « A Traveling-Wave CMOS SPDT Using Slow-Wave Transmission Lines for Millimeter-Wave Application » IEEE Electron Device Letters, vol. 34, no 9, pp. 1094-1096, 2013

[4 ] X. -L. Tang,et al., « Performance Improvement Versus CPW and Loss Distribution Analysis of Slow-Wave CPW in 65 nm HR-SOI CMOS Technology », IEEE Transactions on Electron Devices, vol. 59, no 5, pp. 1279 -1285, may 2012.

[5] Lugo-Alvarez, J., A. Bautista, F. Podevin, et P. Ferrari. «High-directivity compact Slow-wave CoPlanar Waveguide couplers for millimeter-wave applications». In 44th European Microwave Conference, EuMC’14, 1-4. Roma, Italy, 2014. https://hal.archives-ouvertes.fr/hal-01021205.

[6] W. Aouimeur, J. Moron-Guerra, A. Serhan, S. Lepilliet, T. Quemerais, D. Gloria, E. Lauga-Larroze, J.-D. Arnould, C. Gaquière, “A G Band +2 dBm Balanced Frequency Doubler in 55 nm SiGe BiCMOS”, IEEE Silicon Monolithic Integrated Circuits in RF Systems (SIRF), Phoenix, jan 2017.

[7] W. Aouimeur, J. Moron-Guerra, A. Serhan, S. Lepilliet, T. Quemerais,D. Gloria, E. Lauga-Larroze, J.-D. Arnould, C. Gaquière, “A G Band Frequency Quadrupler in 55 nm BiCMOS for Bist Applications”, IEEE International Workshop on Integrated Nonlinear Microwave and Millimetre-Wave Circuits, INMmiIC2017, Autria, April 2017

Contactez-nous

Contactez-nous Plan d’accès

Plan d’accès